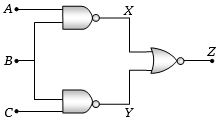

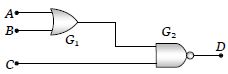

આપેલ પરિપથ કયા ગેટને સમતુલ્ય થાય?

Diffcult

b

(b)The truth table of the circuit is given

(b)The truth table of the circuit is given

Output \(Z\) of single three input gate is that of \(AND\) gate.

| \(A\) | \(B\) | \(C\) | \(X \overline {AB}\) | \(Y= \overline {BC}\) | \(Z= \overline {X+Y}\) |

| \(0\) | \(0\) | \(0\) | \(1\) | \(1\) | \(0\) |

| \(1\) | \(0\) | \(0\) | \(1\) | \(1\) | \(0\) |

| \(0\) | \(0\) | \(1\) | \(1\) | \(1\) | \(0\) |

| \(1\) | \(0\) | \(1\) | \(1\) | \(1\) | \(0\) |

| \(0\) | \(1\) | \(0\) | \(1\) | \(1\) | \(0\) |

| \(1\) | \(1\) | \(0\) | \(0\) | \(1\) | \(0\) |

| \(0\) | \(1\) | \(1\) | \(1\) | \(0\) | \(0\) |

| \(1\) | \(1\) | \(1\) | \(0\) | \(0\) | \(1\) |

Download our appand get started for free

Experience the future of education. Simply download our apps or reach out to us for more information. Let's shape the future of learning together!No signup needed.*

Similar Questions

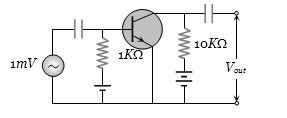

- 1$CE$ એમ્પલીફાયરનો પાવર ગેઈન જ્યારે ઈનપુટ અવરોધ $3\,k\, \Omega$ અને લોડ અવરોધ $24 \,k\, \Omega$ હોય તથા $\beta=6$ હોય ત્યારે કેટલો ?View Solution

- 2$NPN$ ટ્રાન્ઝિસ્ટરમાં કલેકટર પ્રવાહ $24mA$ છે,જો $80\%$ ઇલેકટ્રોન કલેકટરમાં પહોંચતા હોય,તો બેઝ પ્રવાહ ($mA$ માં) કેટલો થાય?View Solution

- 3$AND$ ગેટ બનાવવા માટે કેટલા લઘુતમ $NAND $ ગેટ વાપરવા પડે?View Solution

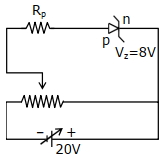

- 4ઝેનર વોલ્ટેજ $8\, {V}$ અને પાવર વ્યય રેટિંગ $0.5\, {W}$ ધરાવતો ઝેનર ડાયોડ આકૃતિમાં દર્શાવ્યા મુજબ ગોઠવેલો છે કે જેથી તેમાંથી મહત્તમ વિદ્યુતસ્થિતિમાન ઘટાડો ધરાવતા સ્થિતિમાન ડિવાઈડ સાથે જોડેલ છે. રક્ષણાત્મક અવરોધ ${R}_{{p}}$ ($\Omega$ માં) નું મૂલ્ય કેટલું હશે?View Solution

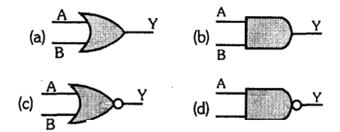

- 5નીચે ચાર લોજીક સંજ્ઞાઓ આપેલી છે. એમાંથી અનુક્રમે $OR, NOR $ અને $NAND $ ગેટસ માટે કઈ સંજ્ઞાઓ છે?View Solution

- 6$5 \times 10^{18}\, m^{-3}$ ઇલેક્ટ્રોનની સંખ્યા, $5 \times 10^{19}\, m^{-3}$ હોલની સંખ્યા, $2 .0\, m^2\, v^{-1}\, s^{-1}$ ઇલેક્ટ્રોન મોબિલિટી અને $0.01\, m^2\, v^{ -1}\, s^{-1}$ હૉલ મોબિલિટી ધરાવતા અર્ધવાહક પદાર્થની વાહકતા(${\left( {\Omega - m} \right)^{ - 1}}$ માં) કેટલી થાય? (ઇલેક્ટ્રોનનો વિજભાર$=1.6 \times 10^{-19}\, C$)View Solution

- 7કોમન એમિટરનો પ્રવાહ ગેઇન $\beta = 100$ હોય,તો આઉટપુટ વોલ્ટેજ કેટલો થાય?View Solution

- 8$A = B = C = 0 $ અને $A = B = 1, C = 0 $ ઇનપુટ માટે આઉટપુટ કેટલો થાય?View Solution

- 9$OR$ ગેટનો આઉટપુટ વોલ્ટેજ $‘1’$ હશે, ...View Solution

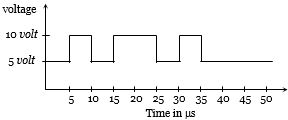

- 10View Solutionનેગેટિવ લોજીક પદ્વિતમાં આપેલ તરંગ માટે નીચેનામાથી શું સાચું થાય?